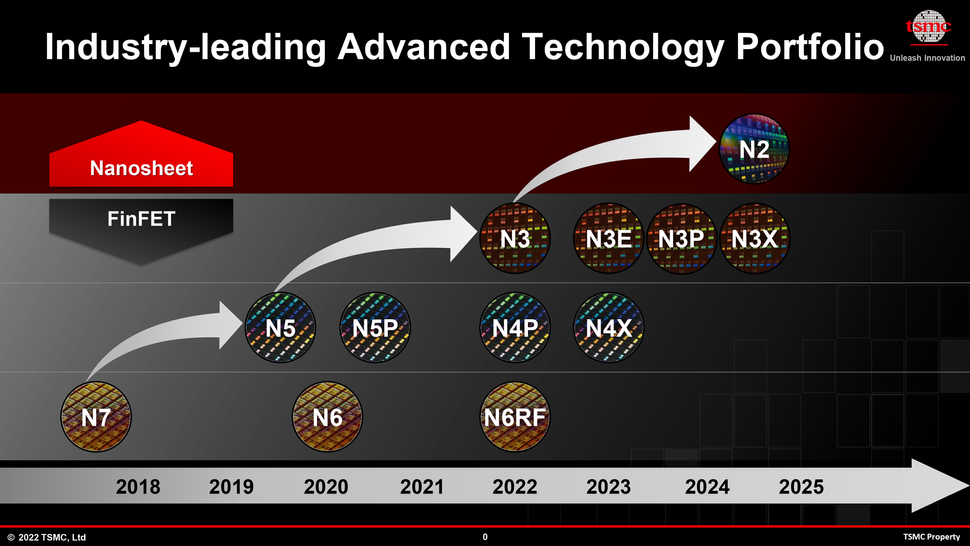

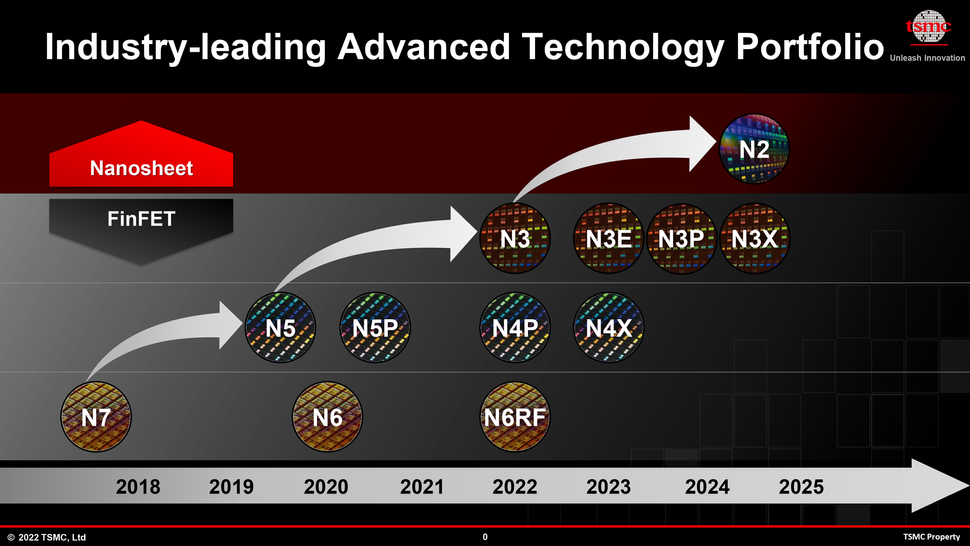

Nye PS5 Pro rygter: Denne gang handler det om process nodes, hvor det endnu er svært at komme til TSMC's 3 nm, idet

Apple har lavet [dyr] aftale med TSMC om at optage 85-90% af TSMC's 3nm produktionen for 2024 til deres fremtidige iPhone, Mac, and iPad. Selv

Nvidia's mindre kort i

5000 serien, der ellers først rygtes at udkomme i 2025, skulle komme i 4nm for de mindre af kortenes vedkommende og kun de største af kortene i serien i som 3nm, hvilket kunne tyde på at der også er klem på 3nm køen i 2025. De samme rygter svirrer omkring

AMD's kommende 8000 serie af CPUer - altså at det kun bliver de største modeller der regnes chance for at komme i 3nm. Om PS5 Pro rygtes det aktuelt:

"the console's chips won't be built on a 3nm process node but likely on the N4P process node, which is a 4nm process node. According to the leaker, there isn't much difference with the N3E 3nm process in terms of power and performance, so going with a 4nm process node isn't going to impact the console's power in any significant way."

-

https://wccftech.com/playstation-5-pro-4nm-process/ -

Det er at regne som en god nyhed, da andre rygter har talt om 5nm process - nyheden kan i hvert fald ind til videre tolkes sådan at Sony tester 4nm og der er en

chance for at Pro kommer i produktion i 4 nm frem for 5 nm. - Som reference er den aktuelle vanilla PS5 lavet på 7nm.

BTW, the devil is in the detail som man siger det. Hvis man undrer sig over hvad P og E efter N3/N4 står for, så er N3 (a.k.a.

N3B) [eller vanilla N3] først out the gate - Det kommer vi, tidsperspektivet i betragtning, efter alt at dømme til at

se i de første Apple N3 baserede produkter.

Næste skridt er bliver

N3E, hvor E'et står for

Effeciency og bla. dækker over lavere grader af EUV (Extreme Ultraviolet Lithography) layers og fraværet af double patterning. Double patterning handler om at behandle chippen to gange med forskellige masker til at opnå mindre og mere komplekse mønstre i chippen. Resultatet er at selve

cellestørrelsen i N3E bliver mere som en N5 - Dermed bliver fremstillingen både hurtigere og med større yield, hvilket betyder at den bliver

billigere, mens den ikke matcher meget store monolitiske chips særligt godt -

Det er således N3E vi kan forvente at se benyttet til især mobile enheder, hvor chippen ikke behøver at være den største i verdenen.

Dernæst begynder det at blive mere interessant, for så kommer

N3P, hvor P'et står for

performance og den version vil få både

højere transistortæthed (via double patterning), flere YUV Layers og dermed

højere performance og/eller lavere strømforbrug end vanilla N3/N3B. Det er den version der rygtes at f.eks.

Apple's M chips ultimativt vil komme til at benytte

i senere MAC's, i hvert fald om ikke andet

EFTER at der formentligt før da udkommer nogle Apple chips på

N3/N3B (tidsperspektivet taget i betragtning). Det er så den P-tier der svarer til at

PS5 angiveligt vil komme til at

benytte P versionen i N4P og forklarer således udsagnet om at "there isn't much difference with the N3E 3nm process in terms of power and performance" [altså N4P vs N3E]

Der er så også den sidste

N3X, som man gerne siger står for "Power", idet denne node gøres mere tolerant over for højere spændinger. Det er

high-end noden. Den giver chipdesignere mulighed for at skrue op for både

strømforbrug og clockhastighed. Det er orienteret imod High-Performance Computing, herunder f.eks.

High-end GPU- og desktop CPUer. Denne node (N3X) sættes først, som den sidste N3 variant, i produktion i

2025, hvilket sammen med den meget samtidige fremkomst af produktionen af

GDDR7 bruges som forklaring på de leaks og rygter der aktuelt er fremme om at f.eks. en

Nvidia's 5000-serie først ser dagens lys i

2025 og ikke i 2024 som man ellers normalt ville have forventet det (hvert 2. år)